16-bit Processor Build - Initial Assembly (cont.)

- rehsd

- Sep 4, 2022

- 4 min read

Updated: Oct 3, 2022

Continued from 16-bit Processor Build - Initial Assembly...

4 September, 2022

I have assembled two new PCBs. One PCB covers add, subtract, carry flag, and zero flag. The second PCB covers shift, rotate, AND, and OR.

I updated my ROM / RAM / Decode PCB due to last-minute design changes and some transposed signal connections.

5 September, 2022

I have reached another major milestone in my project. I now have shift left/right, rotate left/right, AND, OR, add, and subtract working! I now have the hardware substantially complete (well, the first version at least 😁). I have an updated control card coming this week, along with a bus signal indicator card. I expect I will need a single, larger bus board at some point, especially if I want to improve speeds of the system. I also need to make modifications to support interrupt handling (see Interrupt Support for My 16-bit Processor). However, I should have enough pieces in place now to drive a 1602 LCD -- my next video hopefully.

7 September, 2022

I have updated the Control card to use bus transceivers and flash memory (instead of EEPROMs). I removed the LED debug headers and built a separate card to show all control and internal bus values.

9 September, 2022

The new Control card is running. I had to swap out the SST flash with Atmel flash.

10 September, 2022

The processor is now prepped for a 1602 LCD. I have LED bar graphs running from a 6522 VIA on external bus. In the process, I corrected a couple of minor issues with the processor's microcode.

20 September, 2022

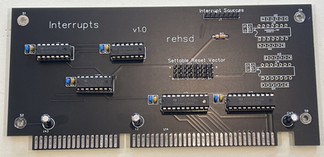

New cards to better support the stack pointer (including previous/next location), interrupts, and connectivity between the internal and external bus.

30 September, 2022

I can now run a 1602 LCD from my 16-bit processor!

1 October, 2022

I have verified functionality of the stack pointer card, which includes a register for the current stack pointer and support to fetch the next or previous stack pointer address. I updated the microcode to support JSR and RTS (TCS was already supported), and everything is looking good. Staring at microcode in Excel for too long hurts the brain. (The Excel file has built-in support to generate the micro-code ROMs directly from the Excel file.)

I have now implemented the micro-code and tested for PHA, PHX, PHY, PLA, PLX, and PLY.

As I was debugging the BNE instruction, I realized the flags register required RES instead of RESB (high instead of low) to reset it. I had it tied to RESB, so it was always resetting. I ran RESB through an inverter to provide RES and now the flags register is properly storing the zero flag. BNE appears to be working.

I am running the processor with LCD on a 250 kHz CLK right now. Attempting 500 kHz fails, but with the mess of wiring I have (on a breadboard), I am not going to complain about it. :)

In the following video, I show an overview of assembling code for program ROMs, creating control ROMs, and how I have been debugging (so many little details to get right).

Update: After a lot of troubleshooting, I found that the LED bar graph on the external data bus was causing reads from the bus to return zero. This was an issue for my LCD code that reads whether or not the LCD is busy. Short version... I removed the LED bar graph on the external data bus. I am now successfully running the processor with the external VIA and LCD with a 4 MHz CLK.

Next Up

Continue to clean up microcode, test, test, test, fix, fix, fix. Interrupt support. I am missing some logical operations (e.g., XOR) that I would like to add.

Then to try some more involved assembly coding and identifying the biggest bottlenecks in the system (could it be ribbon cables?!). :)

Running To-Do List

More to serve as a reminder to myself, below are things I have identified that could be done (changes, fixes, etc.). (✔ indicates completion)

✔ Switch step counter on counter card to falling edge of clock.

✔ Connect the right-side ribbon connector from the counter card to the control card.

✔ Update clock card to put CLK# on the bus.

✔ Update clock card to read HLT control signal and stop clock accordingly.

✔ Develop utility to generate ROM images for control card.

✔ Add an LED indicator to the counter card to show initialization status (ON = initializing, OFF = initialized).

Possibly add pull-down/up resistors to inverter inputs (for control signals). This may be helpful if the control card is not present/running.

Add instruction to swap MSB and LSB of register A (or any register). (thanks, u/Tom0204, for the suggestion!)

✔ Update the '161 counters to use carry-look-ahead instead of ripple mode carry.

✔ Update clock card to pause clock when RESB is low. This was an issue as the reset circuit was counting the number of clocks before switching from the initialization EEPROM to the RAM. Since the reset duration can be adjusted on the clock/reset circuit, the specific number of clock cycles for the reset could vary. It is best if the reset circuit does not start counting until RESB is brought high (i.e., no active reset button push or not initial reset on power on).

Interrupt support.

Keyboard support.

Dual bus board version 2.0 (more slots).

Mouse support.

Video card (version of my card from my 65816 system).

Updated bus bridge card with corrected debug header layout (✔) and possibly logic to filter out processor internal I/O from external bus.

Re-factor arithmetic and bitwise logic PCBs to utilize 74S181 (or HC) ALU/FG.

Add secondary flags register with additional flags in control (F2I) to support updating interrupt flag and not impact other flags.

Add support to read flags to bus and load flags from bus. This will enable writing flags to the stack and retrieving from the stack.

Add masked video write instruction to support transparency. (thanks, u/DockLazy, for the suggestion!)

Upgrade instruction step counter from 3-bit to 4-bit. While mostly unnecessary, it would give me some flexibility for more complicated instructions. Since my instructions can be variable count length, this will not have a negative impact on instructions that do not need the higher number of steps.

Widen the internal bus to support at least 16 more signals (e.g., for Register I, which I use internally for many operations). Two ISA connectors for the cards that need it?! Or some other type of connector/bus system.

...

Comments