Troubleshooting a MicroBlaze UART

- rehsd

- Nov 30, 2021

- 2 min read

Updated: Dec 1, 2021

I am trying to determine why I am unable to communicate out through a UART on my Arty A7-100T. Any suggestions on how to troubleshoot this issue would be much appreciated.

I am using this article as a general guideline: Getting Started with Vivado IP Integrator and Xilinx SDK. If I build a project from scratch, I can get a test message printed to a serial terminal without issue. However, when I attempt to add a UART IP block to the block design of an existing project that I have been working on, I cannot get any output from the UART. I am likely missing something obvious.

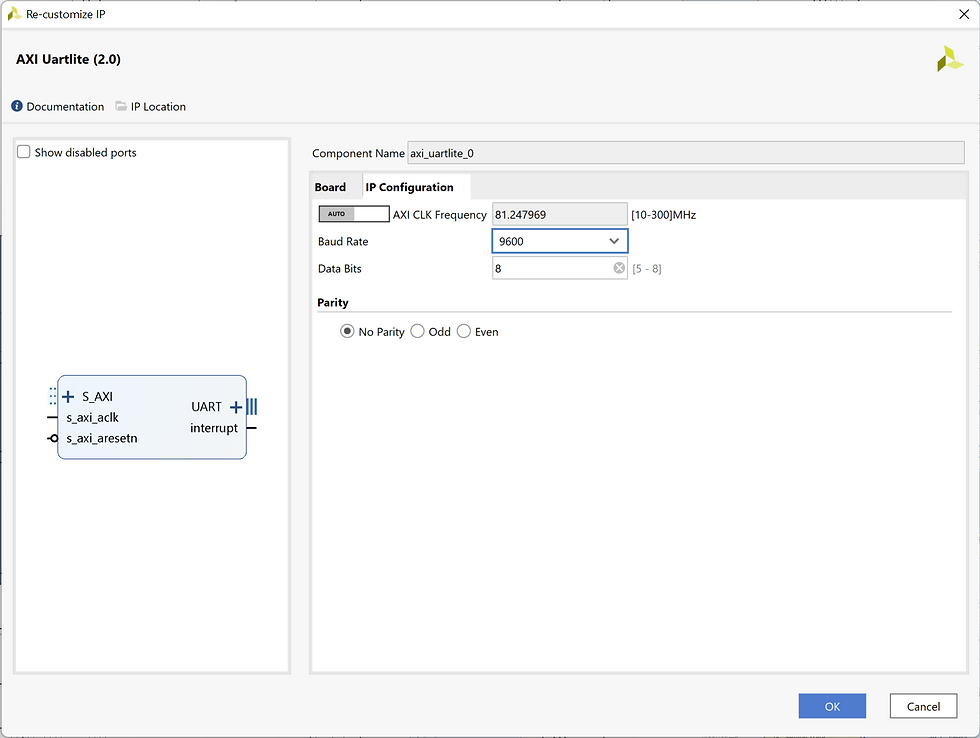

Below are images of the current block design and UART properties.

The Vitis project:

Are there common configuration errors that I should be looking at? Could this be some sort of a clock-related issue?

Update

I appreciate the suggestions I have received from several people about how to troubleshoot this issue. The first suggestion was to verify the Board Support Package settings in the Vitis project. I found that stdout and stdin were set to none. I changed this to axi_uartlite_0. While this didn't resolve my issue, it would have likely been an issue later.

Looking through error and warning messages, I saw this:

Here's the referenced XDC:

This suggested that I might have a problem with constraints (e.g., naming mismatches). I tried a series of different ways to configure the constraints, with no luck. I also removed and re-added the AXI Uartlite IP from the block design. No luck.

As I worked through the troubleshooting process, I found that the pin assignments for the UART were not happening. Here is an image of the pin placement from both a working project and the project that was failing.

This helped me isolate the problem to something in Vivado (and not in Vitis). From there, I took a look at the design wrapper and found that it had no references to any UART-related signals. At that point, I deleted the wrapper and recreated the wrapper from the design. This resulted in a wrapper that looked much better.

I then ran down all the steps in the Flow Navigator (e.g., Synthesis, Implementation, and Bitstream). I exported the hardware, refreshed the hardware in Vitis, and tested out my previous code. Success!

Comments